带石英晶体的振荡电路

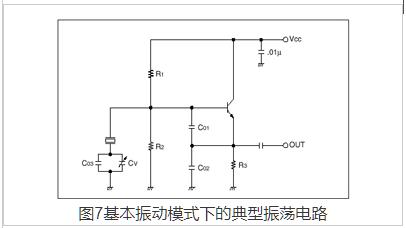

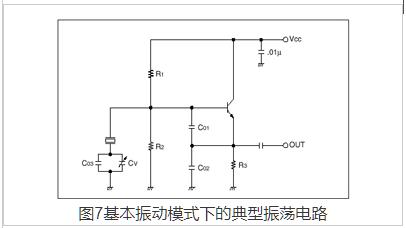

1.典型的振荡电路(基本振荡模式)

典型的振荡电路图如图7所示。

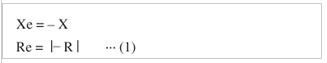

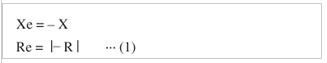

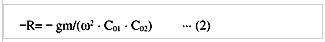

当振荡模式处于稳定状态时,晶体单元Xe的电抗,电路电抗-X,晶体Re的阻抗和电路阻抗-R之间的关系如下:

稳态的简化振荡电路如图8所示。

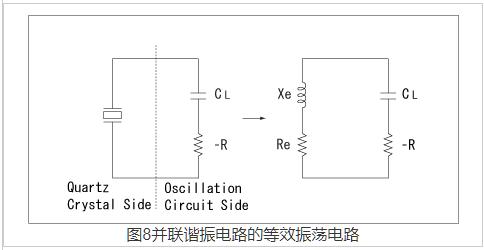

为了获得电路的安全振荡,晶振电路的负电阻必须满足以下等式:-R |

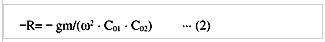

以图7中的电路为例,电路的负阻如下所示:

这里,

gm =振荡级晶体管的互导

=振荡角频率

=振荡角频率

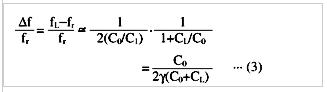

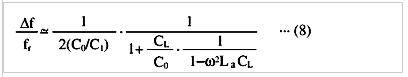

2.负载电容和振荡频率

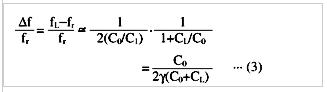

鉴于串联谐振频率= fr

等效串联电容= C1

并联电容= C0

谐振频率(带负载电容CL)= fL

和fL - fr =  f

f

然后,

引入上述等式。

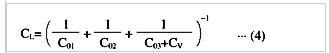

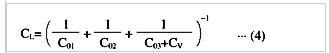

负载电容可视为C01,C02和C03 + CV 的串联电容,如图7所示,包括晶体管和电路图案的杂散电容。

因此,负载电容CL由下式给出。

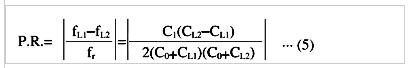

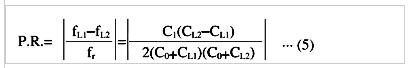

“拉动范围”,即振荡电路的负载电容可以从CL1改变为CL2时的频率变化范围,表示为,

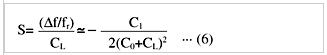

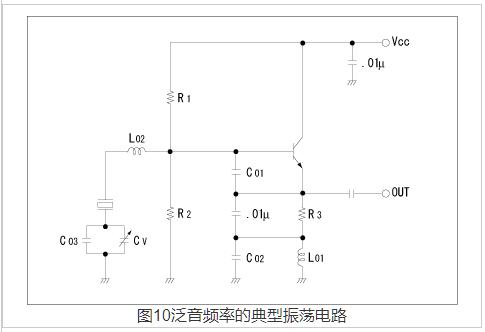

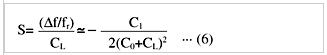

如果给出等效串联电容C1,并联电容C0以及上述CL1和CL2,则可以从上面的等式引出频率变化范围。“拉动灵敏度”是负载电容(CL)附近元件的灵敏度,由下式给出。

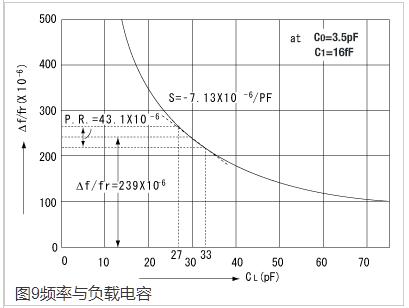

谐振频率与石英贴片晶振负载电容特性如图9所示。

在C1 = 16 pF,C0 = 3.5 pF,CL =的给定条件下计算上述等式(3),(5),(6)的结果30pF,CL1 = 27pF,CL2 = 33pF。

通过应用这种现象,可以通过调节可变微调电容器来将振荡电路的输出频率调整到标称频率,以抵消由于晶体单元的产生偏差和振荡电路中的元件偏差引起的偏差。

尽管等式(6)中的负载电容(CL)的减小将增加器件灵敏度,但是相反地,它也将降低稳定性。

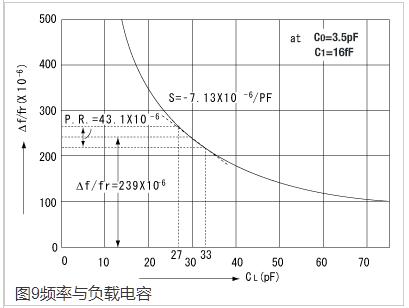

请注意,负载电容的减小将增加启动振荡的难度,因为晶振晶体单元的有效电阻将增加,如公式(7)所示。

3.泛音振荡电路

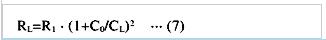

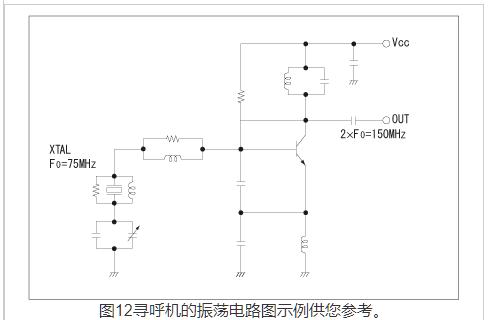

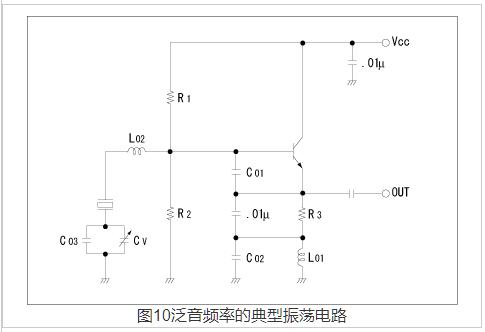

泛音振荡电路的一个例子如图10所示。在具有基波的振荡电路(图7)。相比之下,在该电路两个额外的电感器。

增加的电感器之一(L01:连接到晶体管(Q1)的发射极)包括频率选择电路以及并联连接的CO 2,抑制基波或低振荡以稳定谐波振荡。由L01和C02组成的该环称为选择电路。为了获得选择性,条件是L01和C02的值的配置,使得L01和C02的并联谐振频率 在所请求的谐波频率和较低的谐波频率或基频之间。

在所请求的谐波频率和较低的谐波频率或基频之间。

接下来,将进一步解释该电路的负电阻。

在等式(2)中,如果用 C02 代替,则负阻-R将为 -

C02 代替,则负阻-R将为 -  。

。

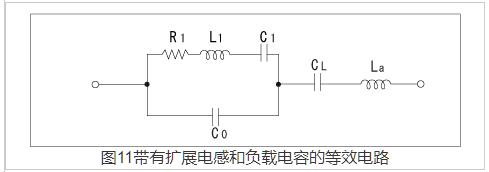

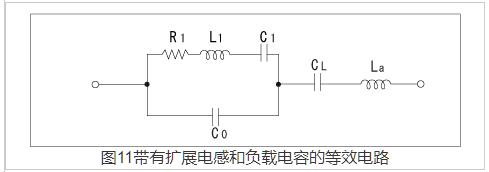

负电阻将与频率的平方成反比地减小。因此,C01和C02必须具有足够小的值在泛音振荡的情况下。在泛音振荡的情况下另一个需要考虑的是石英晶振频率可变范围。在等式(5)中,等效串联电容的值与泛音阶的平方与基本振荡频率的平方成反比,因此频率变化的范围将更窄。C01和C02都会变小,以确保负电阻,使频率调谐更加困难。然而,这一事实也表明,振荡环外的湍流的频率稳定性得到提高。为了确保频率可变范围,通常添加电感器L02。这个电感器L02被称为“扩展电感器”,

在等式(8)中,如果La 0,则诱导等式(3)。

如果在这种情况下添加延伸 电感,请配置CL和La 的值以满足表达式

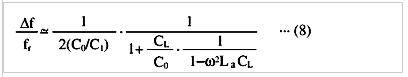

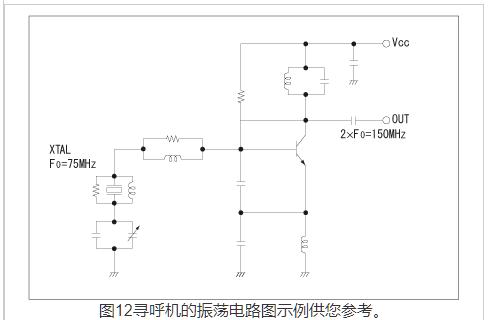

图12显示了寻呼机的振荡电路图示例供您参考。

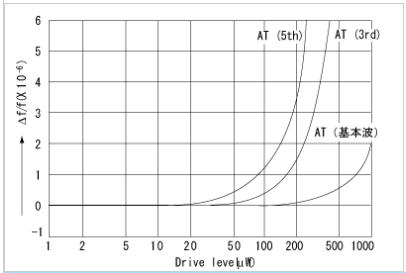

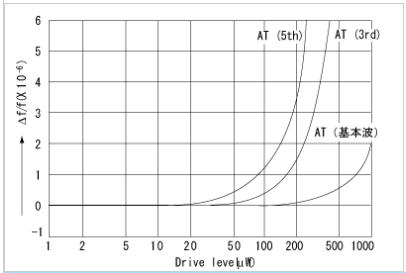

4.晶体振荡的驱动电平

为了确保晶体振荡器的稳定振荡,必须施加一定程度的驱动功率。图13显示了频率如何随驱动电平变化,频移量随着驱动电平的增加而增加。

对晶振装置施加高驱动功率(约50mW)会对其造成损坏。对于在正常振荡电路中使用,优选的驱动功率为0.1mW或更小(最大0.5mW)。

5.设计PCB图案时必须考虑以下几点。

从振荡级到晶体单元的图形长度应该是最小的,以便将振荡环的杂散电容保持在最小。

在振荡回路上放置其他元件和布线图案时,应将杂散容量的增加保持在最小。